コンピュータ・アーキテクチュア第9回

16ビットCPU 8086 の命令体系

(今の64ビットCPUでは命令が拡張されているが基本構造は変らない)

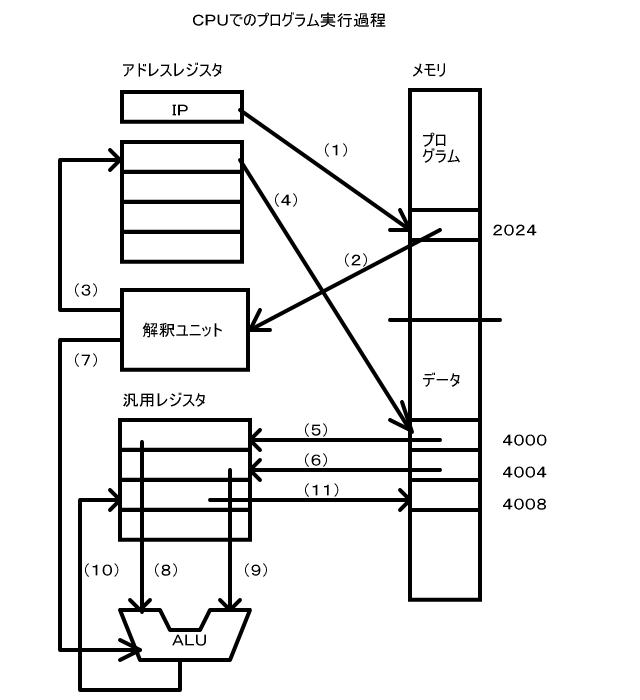

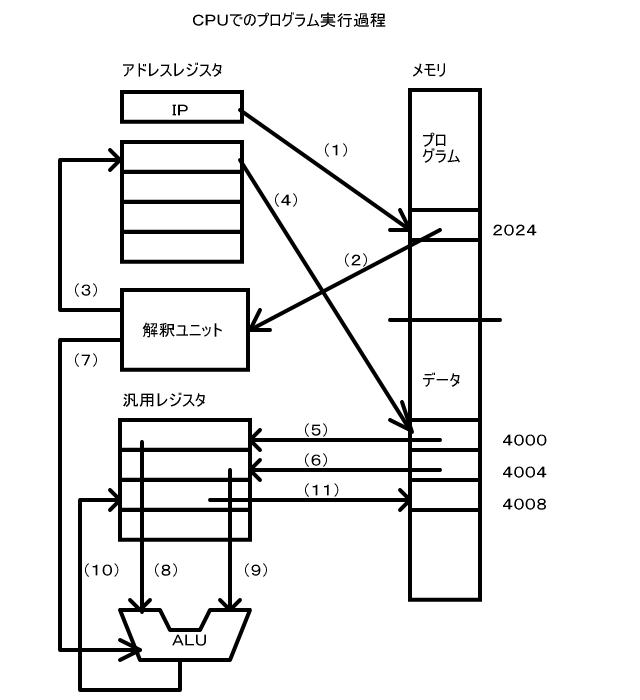

ここで、具体的に、CPUが命令を実行する様子を、簡単な例で説明しましょう。

「4000番地のデータと、4004番地のデータを加えて、結果を、4008番地に書き出す。」

という命令があったとします。

これを、次のように書くとします。( [ ] は、そのアドレスにあるデーを現しますが、詳細は後で説明します。)

[4000] + [4004] −> [4008]

CPUは、次のような順序で命令を実行していきます。

(1) IPレジスタ(次に実行する命令のアドレスを示すレジスタ。)の示すアドレスを、命令読み込み位置として指定する。

(2) 命令を読み込み、解釈する。

(3) データの読み込み位置を示すアドレスレジスタを指定する。

(4) データを読み込むアドレスを指定する。

(5)(6) 指定のアドレスから、データを、汎用レジスタに読み込む。

(7) ALUに指定の演算を指示

(8)(9) 指定の汎用レジスタの内容をALUに送って演算を行う。

(10) 演算結果を汎用レジスタに書き戻す。

(11) 汎用レジスタのデータを、指定のアドレスに書き戻す。

(注)上記の動作は、1つの命令では出来ず、複数の命令を実行することになりますが、煩雑になるので、命令の読み込みは、最初の1回だけ掲げました。

現在のパソコンで使用されているCPUの主流である、Pentium4が、どのように進化してきたのかを表に掲げました。

(もちろん、他の種類のCPUもありますが、ここでは、省略しました。)

| 年代 |

ビット数 |

CPU型 |

トランジスタ数 |

クロック |

| 1971 |

4 |

4004 |

2250 |

0.75MHz |

| 1972 |

8 |

8008 |

3500 |

0.5MHz |

| 1974 |

8 |

8080 |

6000 |

2MHz |

| 1975 |

8 |

8085 |

6500 |

3MHz |

| 1978 |

16 |

8086 |

13万 |

5−8MHz |

| 1982 |

16 |

80286 |

13万 |

6−16MHz |

| 1985 |

32 |

80386 |

28万 |

12−33MHz |

| 1989 |

32 |

80486 |

120万 |

50−66MHz |

| 1993 |

32 |

Pentium |

330万 |

60−266MHz |

| 1997 |

32 |

Pentium? |

750万 |

450MHz |

| 1999 |

32 |

Pentium? |

950万 |

500MHz−1GHz |

| 2000 |

32 |

Pentium4 |

2350万 |

1.3GHz−3.6GHz |

| ? |

? |

★ |

? |

? |

| ? |

? |

★★ |

? |

? |

|

? |

★★★ |

? |

? |

ビット数は、一般的に考えられているビット数である。80486以降、外部バス幅は64ビットになっているが、内部レジスタが32ビットなので、32ビットCPUに分類する。

トランジスタ数、とは、内部の回路を構成する素子で、トランジスタに相当する部分の数をさす。

クロックは、大体のクロックであり、多少の幅がある場合もある。

現在のPentium4 は、それ以前の物より、処理能力が向上しているとはいえ、基本的な設計思想は、80386に於いて提唱されたものを引きついでいる。そのため、80386以降のCPUは、内部処理の形式の変化や、命令の充実、速度の向上などがあるものの、「386アーキテクチュア」と呼ばれている。

86系CPUの命令体系の基本は、8086CPUによって作られ、その後、命令を拡張する形で発展してきたが、ここでは、その基本となる、8086CPUの命令を基本に、CPUでは、どのような命令が実行されているのかを解説していく。

Javaにしても、C言語にしても、どのような言語で書かれたプログラムも、最終的には、CPUの分かる言語「機械語」に変換されてから、実行される。この、各言語を、機械語に変換する作業を「コンパイル」という。

なお、「機械語」を直接人間が書くのは困難なので、機械語を、人間のわかりやすい形式でプログラムできるように作られた言語を「アセンブリ言語」という。

ここのリンクからの書籍コピーを用いてアセンブリ言語の概要を説明します。

8086CPUの命令体系

なお、この命令解説は、CPUの動作を理解するために重要な問題を多数含んでいるので、来週、再来週も、引き続き行います。

第4世代coreアーキテクチュア(2013年) i7

http://www.nikkei.com/article/DGXNASFK0402N_U3A600C1000000/

CPUのまとめ

CPUの構造などについての教材を書いてある人のページリンク

http://www.way-on.com.tw/PCbasal/kiso/cpu6.htm

http://www.takenet.or.jp/~ichirou/shittakaburi/c/language/program.html

http://www.calvadoshof.com/Advocate/2007No03.html

4コアCPU(2006年)

http://pcnomori.blog.fc2.com/blog-entry-139.html

私のページと似ている(鹿児島大学)

http://www.ibe.kagoshima-u.ac.jp/edu/expI/theme13/

AMD2013年のロードマップ(読みこなしの練習に使える)

http://pc.watch.impress.co.jp/docs/column/kaigai/20121121_574241.html

AMD CPUの構造

http://pc.nikkeibp.co.jp/article/news/20121002/1065306/?SS=imgview_sp&FD=-652795730

i5 内部構造の記事(2010)

http://news.mynavi.jp/special/2010/clarkdale/index.html

CPU と GPU

http://ja.wikipedia.org/wiki/Graphics_Processing_Unit

PC用語いろいろ解説 DDR3など

http://kakaku.com/magazine/062/p01.html

X86-64アーキテクチュア(分岐予測)(2002年)

http://news.mynavi.jp/news/2002/06/27/10.html

タイトル arch9 宛先 fujiki.kougei@gmail.com

宛先 fujiki.kougei@gmail.com

タイトル arch9

課題:

(1) CPU進化の表の最後の部分の ★ ★★ ★★★ の部分には、どのようなCPUを入れたらよいか。

(2) 一般に、メモリ上では、プログラムとデータは、別の領域に置かれる。なぜ、そのようにするのか。一緒にすると、どのような問題があるのか、考えて述べなさい。

(3) 上の図に書かれている略号の、 IP とは、何をするものか。ALUとは、何をする物か、説明しなさい。